# The Easy Way to Achieve ECO Success

# **ScanChainECO**

# Automatic Scan Chain Fixing Optimized for Best Turnaround Time and Test Coverage

ScanChainECO Datasheet DS-DFT-01

ScanChainECO utilizes an innovative algorithm to assist design teams in efficiently accomplishing scan chain fixing tasks and minimizing test coverage loss resulting from functional ECO. Based on user's design changes, ScanChainECO modifies the original scan chain netlist to create a revised netlist that accommodates the updated logic function.

## **Solution Benefits**

- · Short turnaround time for designs of all sizes and complexities

- · Ease of use and optimized patch for optimal scan chain results

- A Plug-and-Play tool easily integrated with 3<sup>rd</sup>-party design flows

## **Introduction to Scan Chain Fixing**

Scan chain fixing is a critical step during functional ECO (Engineering Change Order), which is an incremental design method used to revise existing ASIC designs. Once the RTL code is revised to change the ASIC function, the ECO process modifies a portion of the existing netlist to align with the revised ASIC function while preserving the integrity of the remaining netlist. ScanChainECO adds scan DFFs to newly added registers in the revised design and creates scan chains to maintain test coverage.

Traditionally, DFT engineers must mitigate the scan chain loopholes created during a functional ECO task. Since scan chains and test patterns are typically generated by ATPG tools, DFT engineers lack an effective means to

make necessary modifications based on the changes reported in the ECO patch. They either recreate both the scan chains and test patterns, which leads to a complete waste of previous design efforts, or choose to ignore the newly added flip-flops, resulting in reduced test coverage.

ScanChainECO empowers designers to efficiently perform scan chain fixing tasks in response to the changes made to registers or flip-flops within the design logic.

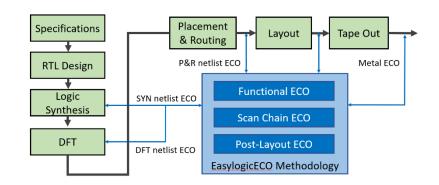

Figure 1: Scan chain fixing needs across design phases

ScanChainECO Datasheet DS-DFT-01 May 2024

## ScanChainECO Design Flow

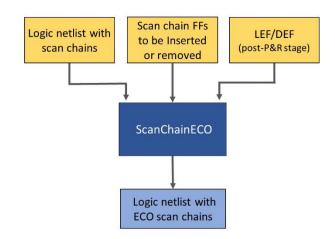

The scan chain fixing process begins with a precise analysis of the original scan chain netlist and the necessary changes. ScanChainECO then modifies the scan chains according to user's design constraints. It seamlessly integrates with user's existing ASIC design tools, creating a complementary flow for efficient collaboration.

The figure on the right illustrates the ScanChainECO tool flow, where:

- The input for scan chain DFFs can either be the ECO report generated by a 3<sup>rd</sup>-party ECO tool or a list created manually by the user for a specific ECO case.

- The ECO scan chain represents the result of the modifications made to the original scan chain netlist.

## ScanChainECO Features

#### **SDFF Selection and Conversion**

Converts regular DFFs into the necessary SDFFs for insertion into the scan chain.

## Scan Chain Stitching, Removal and Balancing

Stitches SDFFs into the original scan chain while disconnecting unnecessary SDFFs. Customizes the chain length based on user's DFT constraints to meet the requirements of the test plan, enabling increased test coverage without compromising testing costs.

## **Support for Advanced Design Requirements**

Ensures compliance with user's design rules while implementing scan chain revisions. Identifies multiclock domains, multi-power domains, and hold time violations and applies necessary adjustments, such as isolation/level shifter cells or lockup latches.

## Physical-Aware ECO Algorithm

Utilizes the physical information provided by the user to

enhance the timing of the scan chain.

### Multiple Types of Post-Mask ECO Resource

Resource options for a post-mask ECO task include spare cells, gate arrays, and filler cells. When combined with physical information, optimizes the delay of scan chains by considering cell function and estimated wire delay.

### **Versatile Design Flow Support**

Supports various ECO flows for introducing changes of FFs, including 3rd-party ECO flow, manual ECO flow, and EasylogicECO flow. It utilizes standard formats for input/output data, enabling seamless integration with mainstream design flow.

### **Command Line Script Operations**

Script-based operation is simple, easy to learn and debug. It only requires modifying specific script fields when migrating to other projects.

# **Technical Support**

For more information, please visit <a href="https://www.easylogiceda.com/en">https://www.easylogiceda.com/en</a> or email <a href="mailto:info@easylogiceda.com/en">info@easylogiceda.com/en</a> or emailto: <a href="mailto:info@easylogiceda.com/e

#### Copyright Notice and Proprietary Information

Copyright © 2022-2024 by Easy-Logic Technology Limited. All rights reserved. Easylogic products and all associated documentation are proprietary to Easy-Logic Technology Limited. Reproduction, modification, or distribution of Easylogic products or the associated documentation without a written consent is strictly prohibited. Easylogic product names are trademarks of Easy-Logic Technology Limited.