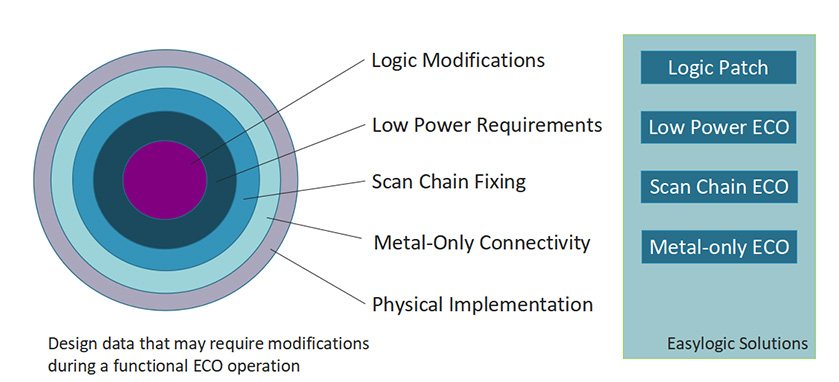

Patch Logic Generation从 RTL 代码的修改开始。这些 RTL 改动会在功能验证、时序延迟、DFT以及金属连线等多个环节产生连锁影响。Easy‑Logic 提供了一套稳健的解决方案,能够生成最小最优化的补丁逻辑,并对下游受影响的设计阶段进行优化。

奇捷科技的 EasylogicECO 采用独创的全自动算法,可以快速生成最小、最优化的补丁逻辑。该补丁不仅满足 RTL 级别的功能修改需求,还兼顾多项设计约束——支持扫描链拼接更新、保持低功耗设计约束、在生成补丁时同步考虑时钟树结构与布线延迟等物理实现因素。

EasylogicECO 的解决方案功能强大且易于使用,运行时间短。其目标是帮助设计团队在无需反复迭代的情况下,最快完成从 RTL 更改到post‑layout阶段的时序收敛任务。快速的完成周期还可以进一步让设计人员有余地尝试不同的 RTL 编码方式,以寻找最合适的 ECO 方案,显著提升 ECO 成功率。

ECO 成功的关键在于尽可能保留现有设计网表,使其改动最小。EasylogicECO 正是遵循这一原则:精准定位需要修改的信号,生成最小补丁,与现有设计流程无缝集成,在保持时序收敛的同时节约时间与资源,交付可靠的设计结果。

在上述三个关键流程中,奇捷科技的 Functional ECO 解决方案为用户提供以下价值与优势:

-

生成补丁小

奇捷科技的 EasylogicECO 采用专利全自动算法,在尽可能保留原有网表的前提下,自动生成最小最优化化补丁逻辑。系统会精准定位需要改动的节点,充分利用设计中未使用的备用资源,仅在极少数金属层上进行修改,从而实现高效的布图布线(P&R)收敛并保持时序完整。

该方案通过最小化的改动,最大程度降低对已有设计的影响,确保设计完整性与可靠性。

-

运行时间短

ECO 的整体交付周期受以下关键因素决定:设计准备时间、工具运行时间、P&R运行时间以及结果验证时间。EasylogicECO 能够自动生成最小化补丁并实现高度模块化的操作,从而显著加速 P&R 流程,使各阶段验证能够快速完成。

这种全链路的优化方法确保了 ECO 流程的每一步都兼顾速度与可扩展性,最终大幅缩短整体交付时间。

-

与现有设计流程无缝集成

只要使用标准的输入/输出格式,EasylogicECO 即可嵌入用户现有的设计流程,无需更换任何工具。即插即用的方式让用户能够继续使用已有的设计平台资源。

EasylogicECO 旨在帮助用户快速上手。通过基于模板的自动化脚本以及对所有应用场景的全面覆盖,用户只需在模板中填写设计信息并启动 ECO 任务,无需繁琐的环境配置。