Introduction to Easylogic Functional ECO Solutions

A functional Engineering Change Order (ECO) involves the following three major processes, each crucial for achieving an efficient and effective implementation:

The patch logic creation process begins with making RTL changes. These modifications have ripple effects across functional verification, timing delays, DFT (design-for-test), and metal connectivity. The quality of the patch, including ECO point locations and the size of patch logic, can significantly influence the design schedule.

Easy-Logic provides a robust solution that produces the smallest patch logic and optimizes all affected design areas downstream.

A metal-only post-layout ECO involves making changes to a layout design that is either near completion or already signed off. The patch logic is restricted to metal connection fixes using spare resources, which are specifically reserved for ECO purposes. The success of the ECO process often determines the fate of the chip.

Easy-Logic’s physical-aware solution generates highly optimized ECO patches, enabling smooth P&R closure with the minimal possible metal layer changes.

DFT changes are crucial for the success of functional ECO. Since scan chain logic is automatically generated by DFT tools, designers often have to put in a great deal of effort on handling scan chain changes to avoid any loss of DFT coverage.

Based on user’s patch logic, the Easylogic solution automatically revises the scan chain netlist to accommodate the updated logic function.

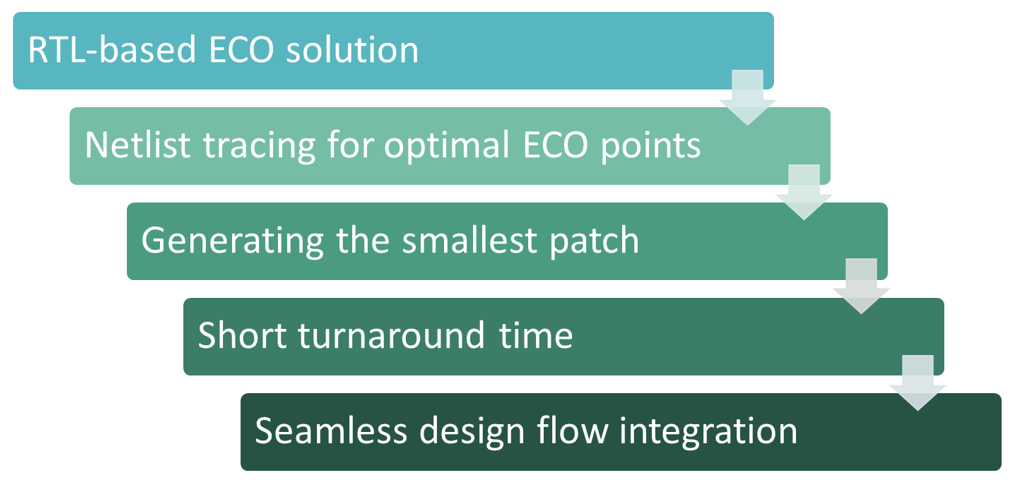

Across all three major processes, Easylogic solutions provide users with the following benefits:

Generating the Smallest Patch

The Easylogic solution leverages a unique algorithm to meticulously trace the original netlist, enabling the identification of optimal ECO points for efficient design modifications. It also employs a specialized optimization algorithm designed to adapt seamlessly to a wide range of designs, ensuring robust and reliable performance across different scenarios. Furthermore, the solution provides extensive constraint options, allowing users to specify various design requirements with precision. This combination of innovative tracing, optimization capabilities, and customizable constraints ensures that Easylogic delivers tailored and high-quality results for complex ECO challenges.

Short Turnaround Time

The total ECO turnaround time is determined by several key factors: design preparation time, tool runtime, downstream P&R runtime, and result verification time. The Easylogic solution is specifically engineered to efficiently handle design sizes of up to 5 million instances with minimal impact on tool runtime. Additionally, its ability to generate compact, physical-aware patches significantly accelerates the downstream P&R process, enabling swift completion. This comprehensive approach ensures that each stage of the ECO flow is optimized for both speed and scalability, ultimately reducing overall turnaround time.

Seamless Design Flow Integration

Easylogic can be integrated with the user’s design flow easily, as long as the tools uses standard input/output format. There’s no needs to replace any tools, and its plug-and-play integration allows users to maintain their existing investments in the design flow.

Another benefit is the quick user ramp-up. Easylogic uses template-based scripts to operate, and there are templates to cover various application scenarios. Users only need to fill out the templates with their design flow information before launching their Easylogic jobs.

In all three ECO processes, the critical success factor lies in preserving the existing design as much as possible and minimizing the size of the ECO patch. Easylogic provides a distinct design solution tailored for each application scenario, seamlessly integrating into the user's existing ASIC design flow. For more information and to access the relevant solution, please click on the image below.

What is a functional ECO tool for?

A functional ECO tool modifies the logic function of the chip in a later stage of the design process, usually after layout and routing, or even after masking. Logic function of the APR netlist needs to be modified.

What are the application scenarios of functional ECO?

Application scenarios include improving chip performance, adding new features, or fixing design errors, whenever it is necessary to change the logic function of the chip design.

In which chip design phases can functional ECO apply?

Functional ECO can be used at any design stage, even after tape-out. But the ECOs differ in how the changes are implemented. There is usually no strict limitation on available resources when ECO is carried out before layout complete. However, for the ECOs after layout complete, only those spare resources reserved for ECO can be used. In addition, since the number of spare resources is limited, there is also a limit on the scale of functional change.

Why is functional ECO a critical step in the IC design flow?

Changing logic functionality by adding a netlist patch to the existing netlist can save a lot of project time. Resynthesizing the netlist from the revised RTL to add new logic functions, subsequently going through the entire ASIC design flow all over again, is time consuming.

Can EasyECO fix my broken scan chain?

Yes. Test circuit such as scan chains and MBIST will not be affected during the ECO process. Based on the needs of the new netlist, EasyECO generates SDFF(s) and also adds the SDFF(s) to the scan chain.

To learn more, please refer to the AppNote "Performing Scan Chain Fixing during Functional ECO Process" under the Resources section of our website.

Does EasyECO consider timing in its ECO flow?

Yes, EasyECO results are optimized for shortest paths. Instead of calculating the delay of each cell unit, EasyECO selects appropriate patch logic based on logic level, the most appropriate spare units based on their physical locations, and clock signals from the clock tree for each generated test register based on the required scan chain function.

To learn more, please refer to the white paper "RTL-Based Full-Module Functional ECO Methodology" under the Resources section of our website.

The RTL signal is removed from my gate-level netlist, can EasyECO locate that ECO point?

Yes, EasyECO utilizes a unique reverse engineering analysis technology to identify signals that were removed during RTL synthesis, or scattered boundary signals, from the gate-level netlist. This enables the selection of the best ECO Point, ensuring successful completion of the ECO task.

What spare cell types does EasyECO support for post-mask ECO?

EasyECO utilizes standard cells, spare cells (including filler cells and gate array), and replaced standard cells to construct patch circuit, and optimizes the patch for better timing results based on the physical information of the spare cells provided by the user.

What are the benefits provided by EasyECO?

EasyECO helps the design team complete ECO tasks in the shortest turnaround time, avoiding delays in the design cycle. EasyECO uses a breakthrough RTL-based Functional ECO algorithm to effectively perform automatic, minimal logic function changes on the netlist to ensure that the changed netlist is consistent with the revised RTL function.

To learn more, please refer to the white paper "RTL-Based Full-Module Functional ECO Methodology" under the Resources section of our website.

What technical parameters do I need to provide to EasyECO?

Input files:

1) RTL design

2) Gate-level netlist (Verilog)

3) Standard cell library (Liberty)

Required input files according to specific the design requirements:

1) SVF or VSDC file

2) Physical design files (DEF, LEF)

EasyECO output files:

1) A netlist that satisfies the ECO function

2) Third-party tool scripts that perform the ECO function downstream

How does EasyECO work?

EasyECO automatically modifies the corresponding gate-level netlist according to designer’s functional changes of the RTL code, so the modified gate-level netlist has the same function as the modified RTL code. EasyECO changes the connections of standard cells of the gate-level netlist, adding new cells or deleting old cells, and finds the minimum scale of logic change.

To learn more, please refer to the white paper "RTL-Based Full-Module Functional ECO Methodology" under the Resources section of our website.

What kind of disruptive technology does Easy-Logic bring to the design industry?

EasyECO offers significant advantages over traditional ECO solutions, including a highly efficient algorithm that improves the utilization of spare resources and speeds up total operations.

Notably, EasyECO enables a significantly larger scale of functional ECO, providing a new level of capability to the ASIC design community. Test results indicate that EasyECO requires on average 30% fewer instance resources compared to traditional solutions, with some cases achieving a reduction of 10 times or more. Tool run time is also over 10 times faster, with speed improvement increasing as the design scale grows larger.

How does EasyECO support advanced process technology?

EasyECO considers the characteristics, and design requirements, of advanced processes 10nm and below and performs additional logic and physical optimizations.

How can I find the sales/support channel in my area?

The contact information for each region is shown under the [Contact] web tab.

Which operating systems does EasyECO support?

1) 64-bit Linux workstation, kernel version not lower than 2.6 (Centos 6/7, ArchLinux, RedHat, SUSE, Ubuntu)

2) At least 64GB RAM memory

3) At least 100GB free disk space

4) Multi-core CPU processor

What technical services does Easy-Logic provide?

Our team of Applications Engineers are readily available to assist you with any technical queries through multiple channels including email, SMS, social media platforms, and VoIP. In addition to this, our technical support services include providing comprehensive online training and guidance for software installation. To initiate a technical discussion with us, please send us an email at info@easylogic.hk.

How to participate in EasyECO training courses?

Please check out the training schedule on the [Events] webpage and register. Events webpage is under [Company] web tab.

Training courses are delivered either in-person or online.

Can I talk to an Applications Engineer about my current ECO difficulties?

We welcome you to discuss any design-related issues you may have with our team of Easy-Logic FAEs.

You may send us an email request at info@easylogic.hk, or alternatively, use the Contact Us form available under the [Contact] web tab to describe your questions. Our FAEs are available to assist you through various communication channels such as email, instant messaging, or video conferencing. We look forward to hearing from you.